## IJRETS: International Journal Of Research In Engineering, Technology And Science,

Volume XIII, Issue VIII, November.2020, ISSN 2454-1915, www.ijrets.com, 1st online international conference on informatics, robotics, construction & communication, 2020

## DESIGN CONSIDERATION OF A HIGH EFFICIENCY FULL BRIDGE SINGLE STAGE CONVERTER WITH IMPROVED OUTPUT

K.R.Shanmuga Vadivu[1], M.Ahalya[2], J.Jeeva[3]

[1] Assistant Professor, EEE Department, Peri Institute of Technology. [2, 3] Third Year Students, EEE Department, Peri Institute of Technology.

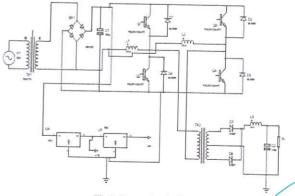

Abstract— This paper explains the single-stage circuit topology consists of of full-bridge isolated dc—dc converter combined with two input inductors and two input diodes connected to the mains network, in order to obtain an isolated ac/dc switch mode power supply, with sinusoidal input current. Consequently, circuit current is equally distributed by using proposed topology of four-bridge transistors which is made up of four input parallel boost power factor correctors (PFCs). Better power factor correction and output voltage regulation is ensured by the use of the four-bridge transistors with galvanic isolation that makes this topology unique, which also contributes to improve the converter efficiency. A maximum efficiency of 94% was obtained.

Keywords— Full-bridge converters, input current shaping, low-distortion input current, single-stage power factor correctors (PFCs).

## I. INTRODUCTION

switch mode power supplies (SMPSs) with galvanic isolation, having the capability to provide the improved power factor correction (PFC) is a eminent characteristic. This PFC topology requires the input bridge rectifier additionally followed by a boost converter circuit to improve the characteristics of the converter [1-3]. For high level of power conversion, the two stage operation is considered here with input converter and full-bridge isolated dc-dc converter results with the inherent characteristics of high cost and the possibility to achieve the very high efficiency in each stage of power conversion. Efficiency is taking major part to assure the better converter operation at any unnecessary conditions. It concluded that, to obtain a overall efficiency is always greater than 95% is mandatory for giving better efficiency greater than 97.5%, which is difficult to achieve and also expensive to obtain, when the second stage is a fullbridge converter[4]-[10]. These techniques were permitted to obtain good input current wave shaping with lower harmonic distortion and efficiency higher, >95%. However, to perform also high-frequency isolation and output dc voltage regulation isolated dc-dc converter ratings of the power transistor and diodes increase considerably, there by

K. R. Shanmuga vadivu working as assistant professor in the Department of Electrical and Electronics Engineering, Peri Institute of Technology, Chennai. (e-mail: <a href="mailto:pradikshavadivu@gmail.com">pradikshavadivu@gmail.com</a>).

M.Ahalya and J.Jeeva are third year students in the Department of Electrical and Electronics Engineering, Peri Institute of Technology, Chennai. (e-mail: <a href="mailto:manoahalya27@gmail.com">manoahalya27@gmail.com</a>, jeevaj5668@gmail.com).

raising the cost of these solutions to values that can be even higher than those observed in the two stages topology [11-15].

Simultaneously, the operation of input current shaping and output voltage regulation could be achieved by using these topologies without using any additional transistors. However, these topologies are not designed in terms of additional components and current distribution in the bridge transistors. For example, in the topologies presented in, only two parallel input boost converters are provided using the low-side transistors, which leads to asymmetrical current distribution in the bridge transistors causing, in these transistors, a high current stress. An input bridge rectifier is also needed for these topologies. For the topologies proposed in, only one input inductor is used, but this inductor and the two low-side transistors have to support the maximum input current Fig 1. On the other hand, the topology presented in uses two inductors for half of the maximum input current, which means that, each low-side boost transistor needs only to support half of the maximum input current, thereby reducing the current stress in these transistors.

## II. CIRCUIT DIAGRAM

Fig 1. Power circuit diagram

UP. R. PALSON KENNEDY

K. R. Shanmuga Vadivu, M.Ahalya, J.Jeeva

**PRINCIPAL**

PERI INSTITUTE OF TECHNOLOGY Mannivakkam, Chennai - 600 048. 1